ATLAS Upgrades@UCL

To further investigate the key open questions in High Energy Physics, it is planned to run the LHC at a much higher intensity, with the aim of increasing the amount of data collected by a factor of up to 10 compared to what has been recorded until the mid-2020s. This High Luminosity programme (HL-LHC) required substantial upgrades to the LHC, to be able to reach approximately 200 collisions occuring simultaneously in the ATLAS detector every 25 nanoseconds, an order of magnitude more than the ATLAS detector was originlly designed for. This meant that significant upgrades to the ATLAS detector were necessary to cope with the large increase in data volumes and complexity of events. The UCL group plays a leading role in these upgrades, specifically in the following areas:

Global Hardware Trigger

Proton bunches collide in the ATLAS detector at a rate of about 40 million per second, but we can only write out around 10000 of these events. The selection of these events is carried out by the trigger. The fast and accurate performance of the trigger to select the small fraction of interesting events, whilst rejecting the large number of background events, is vital for the success of the ATLAS experiment. The ATLAS Global Hardware system ("Global") is a totally new system that is under development/construction for the HL-LHC era. It will absorb and process 50Tbps of data and, within a few micro-seconds, has to reduce the rate of events from 40MHz to 1MHz, i.e. select only 1 event in 40 (on average). The UCL ATLAS team has a leading role in several aspects of the project: (a) developing fast Machine Learning algorithms to be deployed and run on the FPGAs of the Global electronics; (b) developing the "hypothesis testing" firmware block (the last step in the processing, which combines all the information gathered about an event to decide whether to keep it or not); and (c) the offline simulation framework for the Global system.

UCL has also taken a leading role in the NextGenTriggers project, with Prof. Nikos Konstantinidis co-leading the task of developing novel, ultrafast ML algorithms for the Global hardware, as well as evaluating the latest industry hardware for optimizing the performance of Global and maximizing the physics reach of ATLAS at HL-LHC.

Recent/representative public results:Tracker readout

UCL has longstanding experience and is one of the leading groups in data acquisition (outputting the data from the hundred of millions of readout channels that make up the ATLAS detector). The latency and bandwidth requirements of the new upgraded Innter Tracking detector requires the use of custom application-specific integrated circuits (ASICs) and modern field-programmable gate arrays (FPGAs), UCL is a pioneer at exploiting such technologies to meet the exacting future data acquisition demands of the ATLAS detector.

Tracker design, simulation & performance studies

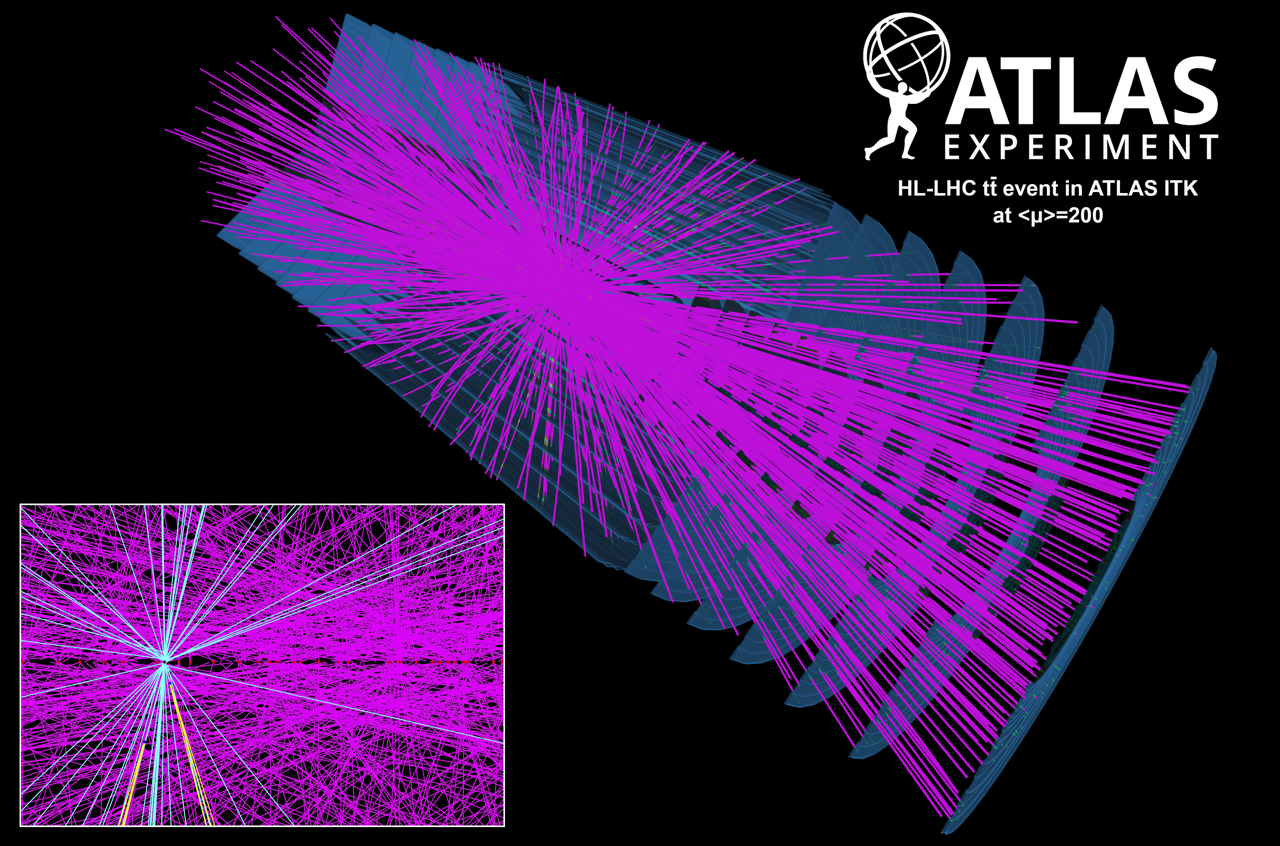

A tracker should be: cheap, massless, 100% hermetic & efficient, and have infinite granularity, bandwidth & lifetime ... When optimising the design of the upgraded Inner Tracking detector, it is necessary to balance these competiting requirements, for which a detailed simulation of the upgraded tracker is essential. To motivate the choices made, predictions of the physics reach are made for the different design options based on this simulation, which includes the conditions expected in the HL-LHC, along with optimised algorithms and analysis selections.

- Technical Design Report for the ATLAS ITk Strip Detector

ATL-COM-UPGRADE-2016-040

- ATLAS Phase-II Upgrade Scoping Document

CERN-LHCC-2015-020 ; LHCC-G-166

- Letter of Intent for the Phase-II Upgrade of the ATLAS Experiment

CERN-LHCC-2012-022 ; LHCC-I-023

- European Committee for Future Accelerators (ECFA) Workshops

ECFA 2016

ECFA 2014

ECFA 2013

Left: A simulated tt̄ event at average pile-up of 200 collisions per bunch crossing, with an upgraded tracker layout covering also the very forward region. Right: A modern ATCA readout shelf

Key Academics

Prof. Nikos KonstantinidisDr Andreas Korn

Dr Tim Scanlon

Leadership Positions

Prof. Nikos Konstantinidis NextGenTriggers project, WP2.1 co-lead 2024-2028Dr Andreas Korn ITK Simulation & Performance - Convener 2013-2016